HOME > ニュース > AV&ホームシアターニュース

公開日 2019/03/18 17:51

ソニー、裏面照射型のグローバルシャッター搭載CMOSセンサー「Pregius S」を開発

高効率な産業システム実現へ

ソニーは、歪みのない高い撮像性能と小型化の両立を実現するという、独自の裏面照射型画素構造によるグローバルシャッター機能搭載CMOS イメージセンサー技術「Pregius S(プレジウス エス)」の開発に成功したことを発表した。

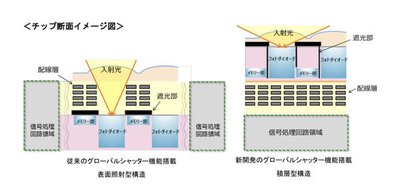

産業の高度化、工場のスマート化・自動化の流れを受け開発された、より高精度で高速な処理が求められる製造・検査・物流などの産業機器向けの製品。グローバルシャッター機能搭載CMOSイメージセンサーでは、フォトダイオードの隣に形成したメモリー部に一時的に電荷信号を蓄えることで、行毎の読み出し時間のずれによる画像の歪み(フォーカルプレーン歪み)を解消している。

表面照射型CMOSイメージセンサーは、フォトダイオードを形成するシリコン基板の上に配線層があり、メモリー部に一時的に蓄えた電荷信号を漏れ光から保護するための遮光部を形成しやすいメリットがあった。そのため、従来のグローバルシャッター機能搭載のCMOSイメージセンサーは、表面照射型画素構造が採用されていた。一方表面照射型では、フォトダイオード上部の配線が入射光の妨げになることが、画素小型化の課題となっていた。

これに対し、感度特性に優れる裏面照射型でグローバルシャッター機能を実現する独自の画素構造を開発することで、小型化の課題を解決したという。通常は画素を微細化すると感度や飽和特性は低下するが、今回の開発ではそれを維持しながら画素サイズ2.74μmの微細化が可能となった。

これにより、従来の1.1型・有効約1,200万画の素表面照射型CMOSイメージセンサー「IMX253」と比較し、約1.7 倍の高解像度化を実現。製造・検査・物流などにおいて、対象物をより広範囲、高精度に測定・検査することが可能になるという。

また、裏面照射型画素構造が持つ配線レイアウトの自由度の高さにより、従来比約 2.4倍の高速性を実現、測定や検査工程の時間短縮などの大幅な生産性向上に貢献するとのこと。加えて、様々な信号処理回路を搭載できる積層型構造を活用することで、測定・検査画像の必要な部分だけの信号処理などを従来よりも小型で実現することが可能となる。

これにより、後段処理の負荷の軽減や、保持するデータ量の削減などができ、省エネで高効率なシステムの実現に貢献することが期待できるという。

同社は、今回開発した技術を搭載した積層型CMOSイメージセンサーを、積層する信号処理回路の派生展開等も含めて、今後様々な産業機器や高度道路交通システムなどへの採用に向け商品開発を進めるとしている。なお本開発品は、2019年夏以降にサンプル出荷予定。また2019年3月20日から上海で開催される「Vision China Shanghai 2019」において技術紹介される。

産業の高度化、工場のスマート化・自動化の流れを受け開発された、より高精度で高速な処理が求められる製造・検査・物流などの産業機器向けの製品。グローバルシャッター機能搭載CMOSイメージセンサーでは、フォトダイオードの隣に形成したメモリー部に一時的に電荷信号を蓄えることで、行毎の読み出し時間のずれによる画像の歪み(フォーカルプレーン歪み)を解消している。

表面照射型CMOSイメージセンサーは、フォトダイオードを形成するシリコン基板の上に配線層があり、メモリー部に一時的に蓄えた電荷信号を漏れ光から保護するための遮光部を形成しやすいメリットがあった。そのため、従来のグローバルシャッター機能搭載のCMOSイメージセンサーは、表面照射型画素構造が採用されていた。一方表面照射型では、フォトダイオード上部の配線が入射光の妨げになることが、画素小型化の課題となっていた。

これに対し、感度特性に優れる裏面照射型でグローバルシャッター機能を実現する独自の画素構造を開発することで、小型化の課題を解決したという。通常は画素を微細化すると感度や飽和特性は低下するが、今回の開発ではそれを維持しながら画素サイズ2.74μmの微細化が可能となった。

これにより、従来の1.1型・有効約1,200万画の素表面照射型CMOSイメージセンサー「IMX253」と比較し、約1.7 倍の高解像度化を実現。製造・検査・物流などにおいて、対象物をより広範囲、高精度に測定・検査することが可能になるという。

また、裏面照射型画素構造が持つ配線レイアウトの自由度の高さにより、従来比約 2.4倍の高速性を実現、測定や検査工程の時間短縮などの大幅な生産性向上に貢献するとのこと。加えて、様々な信号処理回路を搭載できる積層型構造を活用することで、測定・検査画像の必要な部分だけの信号処理などを従来よりも小型で実現することが可能となる。

これにより、後段処理の負荷の軽減や、保持するデータ量の削減などができ、省エネで高効率なシステムの実現に貢献することが期待できるという。

同社は、今回開発した技術を搭載した積層型CMOSイメージセンサーを、積層する信号処理回路の派生展開等も含めて、今後様々な産業機器や高度道路交通システムなどへの採用に向け商品開発を進めるとしている。なお本開発品は、2019年夏以降にサンプル出荷予定。また2019年3月20日から上海で開催される「Vision China Shanghai 2019」において技術紹介される。